Описание

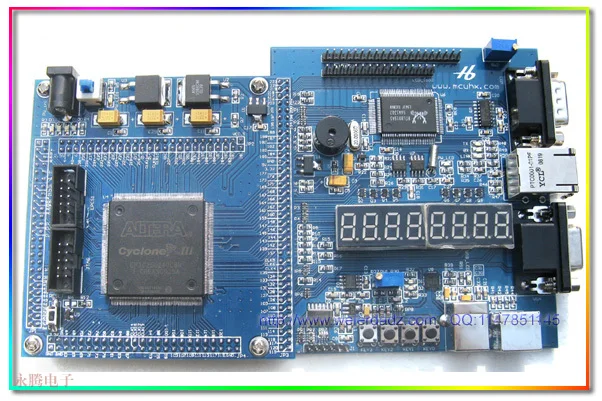

1. Краткое представление основной платы:

Различные основные платы для выбора (основные платы и фотографии см. На странице Интернет-магазина сайта), использование FPGA:

(1) циклонное ядро: EP1C12Q240C8, EP1C6Q240C8;

(2) ядро Cyclone II: EP2C8Q208C8, EP2C5Q208C8, EP2C20Q240C8; ядро Cyclone III: EP3C16Q240C8, EP3C25Q240C8;

(3) SDRAM: 8 Мбайт;

(4) Вспышка: 8 Мбайт;

(5) EPCS1, EPCS4, EPCS16 конфигурации чипов: EP1C6 и EP2C5 основной плате оснащен EPCS1; EP1C12 и EP2C8 и EP2C20 основной плате оснащен EPCS4; EP3C16 и EP3C25 оснащены EPCS16 (то есть емкостью 16 Мб);

(6) предоставляем режимы настройки: JTAG и AS;

(7) две активные часы 50 МГц;

(8) все IO, Avalon автобус, конфигурация pin и так далее вытянуты через четыре ряда контактов, пользователи могут полностью играть свободно, более гибкое расширение;

(9) 4 светодиодный;

(10) кнопка сброса.

Два, Экспериментальная плата V5.0 Введение:

(1) 10 м интерфейс Ethernet: с помощью чипа RTL8019

(2) 8 бит AD аналого-цифрового преобразователя;

(3) 4 канала 8 бит DA DAC;

(4) часы в режиме реального времени;

(5) RS-232 последовательный порт: используется для передачи данных с компьютерами;

(6) интерфейс VGA: прямой VGA и дисплей стыковки, с помощью FPGA для достижения vga-интерфейса протокол может отображать текст, графику и т. д. на дисплее.

(7) PS/2 интерфейс мыши и клавиатуры.

(8) 16*2 символьный ЖК-интерфейс, который может отображать английские символы.

(9) 128*64 матричный ЖК-интерфейс, который может отображать китайский, графический и т. Д.

(10) зуммер.

(11) Интерфейс USB: с помощью USB-UART мостового чипа CP2102, совместимого с USB 1,1 и USB 2,0, максимальная скорость связи составляет 1 Мбит/с, может быть непосредственно использован в соответствии с требованиями скорости связи не часто, такие как промышленное контрольное оборудование, приборы, удобные и практичные; Разработчики не должны понять Протокол USB и драйверы дизайна, так же, как последовательный порт 1. Он имеет преимущества короткого цикла разработки, низкого риска и низкой стоимости. Кроме того, он имеет преимущества небольшого размера, хорошей защиты от помех, стабильной и надежной работы, и нормальный диапазон рабочих температур-40 ~ + 85. CD-ROM, драйвер и пример программы чипа прикреплены к CD-ROM комплекта.

(12) два 4 цифры 7 цифровой трубки.

(13) Память EEPROM на основе протокола iec.

(14) четыре кнопочных переключателя: простой стиль, не погоня за большим, но для поиска простоты, сохранения ограниченныхресурсов IO, для Nios II внешнего ключа ввода, прерывания и других экспериментов достаточно

Характеристики

- Test4

- 4

- Индивидуальное изготовление

- Да

- Номер модели

- EP3C25 V5

- Test1

- 4

Для покупки товара EP3C25 V5 FPGA развитию EP 3C25Q240C8 FPGA развитию нажмите кнопку "купить сейчас".

Если вы хотите купить другой товар из категории электронные компоненты и комплектующие или электроника в наличии то перейдите по ссылкам вверху страницы.