EP4CE6 FPGA SDRAM Совет по развитию штамп отверстие основная плата конкурс электроники артефакт комплект

Цена: $24

есть в наличии

Описание

| |||||

|  |  |  |  |  |

|  |  |  |  |  |

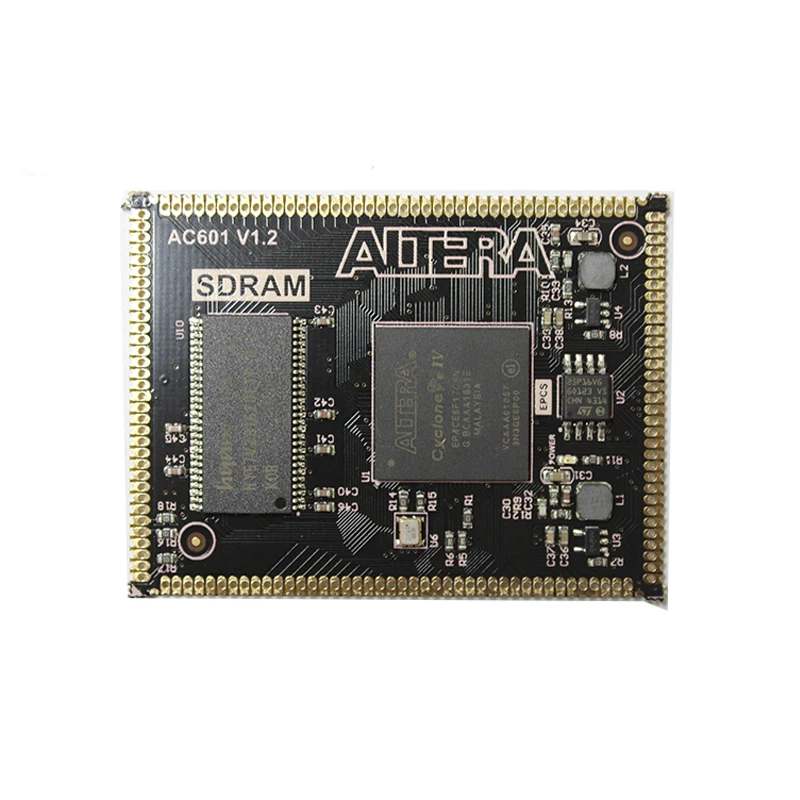

EP4CE6 FPGA SDRAM макетная плата с отверстием для штемпеля основная плата электронный конкурс артефакт комплект

Примечание:

1. В комплект не входит загрузчик. Клиенты должны взять свой собственный загрузчик или купить его в магазине. FPGA не поддерживает прямую загрузку последовательного порта.

2. Эта основная плата в основном предоставляется опытным инженерам для разработки продукта и проекта, без тщательного выбора опыта FPGA. Кроме того, простая оценка сварочных деталей нижней пластины требует определенного количества сварочных способностей.

Технические характеристики:

Размеры: 6*4,5 см

FPGA: EP4CE6F17I7, EP4CE10F17I7 (диапазон промышленных температур)

EP4CE6F17C8, EP4CE10F17C8 (диапазон промышленных температур)

С украшением в виде кристаллов: 50 м

SDRAM: по умолчанию 128 Мбит

EPCS: W25Q16, 16 Мбит SPI вспышка

Источник питания: 3,3 В/500 мА

PCB: 4 слоя, сигнал (сверху), мощность (mid), земля (mid), сигнал

Порт загрузки: JTAG, нет необходимости в качестве интерфейса, непосредственно написать JIC файл через JTAG интерфейс

Гибкое применение:

Основная плата принимает отверстие для штампа и 1,27 мм штыревой разъем два-в-одном интерфейс. Его можно приварить непосредственно к опорной пластине продукта через интерфейс отверстия штампа как компонент для осуществления массового производства продукта. Он также может быть соединен с нижней пластиной с помощью штыревого разъема и гибко заменен.

SDRAM (синхронное динамическое ОЗУ):SDRAM используется в качестве памяти большой емкости для хранения различных данных большой емкости, таких как данные изображения, высокоскоростные данные выборки ADC и произвольные данные формы волны. SDRAM доступен в 256 Мбит, 128 Мбит и 64 Мбит. SDRAM выбирает продукты тайваньской серии Winbond и по умолчанию использует емкость для хранения 128 Мбит (W9812G6).

Флэш-память:

Встроенный 16 Мбит SPI FLASH, для высокой емкости отключения питания без потери памяти, может использоваться для хранения данных конфигурации FPGA (прошивка), полностью эквивалентно Роле EPC. Он также может использоваться для хранения пользовательских данных.

FPGA:

Чип FPGA включает четыре типа поддерживаемых моделей: EP4CE6F17I7, EP4CE10F17I7, EP4CE6F17C8 и EP4CE10F17C8. Среди них E6F17I7 и E10F17I7-устройства промышленного класса, которые могут непосредственно использоваться в промышленном оборудовании. E6F17C8N и E10F17C8N являются устройствами коммерческого класса.

Пользователь I0:Основная плата обеспечивает в общей сложности 154 расширенных IOs, включая

8 GND входов (2/3 в каждом направлении)

1 выходная мощность 2,5 в (2 фута для интерфейса JTAG)

4 входа питания 3,3 В (по 1 в каждом направлении)

4 JTAG конфигурации ввода/вывода

1 конфигурации индикатор выхода

6 тактовый вход IO (может использоваться только как вход)

130 двунаправленный IOs (используется для ввода и вывода)

Кварцевого осциллятора:

Встроенный 50 МГц активный кварцевый генератор обеспечивает стабильный тактовый сигнал для FPGA

Мощность питания:

Вся плата должна только вводить один 3,3 В, выходной ток не менее 500 мА, и бортовой двусторонний импульсный источник питания может обеспечить питание от 3,3 В до 2,5 в и 3,3 В до 1,2 в соответственно. В чипе питания используется высокоэффективный импульсный чип питания с частотой переключения до 1,7 м и эффективностью до 96%.

Характеристики

- Бренд

- ReYeBu

- Состояние

- Новый

- Тип

- Регулятор напряжения

- Номер модели

- EP4CE6 FPGA SDRAM Development Board

- Применение

- Компьютер

- Индивидуальное изготовление

- Да

Для покупки товара EP4CE6 FPGA SDRAM Совет по развитию штамп отверстие основная плата конкурс электроники артефакт комплект нажмите кнопку "купить сейчас".

Если вы хотите купить другой товар из категории электронные компоненты и комплектующие или активные компоненты то перейдите по ссылкам вверху страницы.

![[BELLA] Оригинальный DJM-900NXS2 смеситель фейдер черный Железная панель Вертикальная доска для резки, большой/маленький, буфер обмена DNB1248 DAH3125](https://ae01.alicdn.com/kf/HTB1SAmjbiDxK1RjSsphq6zHrpXan/-.jpg_250x250q75.jpg)