DSP2812 + FPGA + NIOS Совет по развитию TMS320F2812 EP2C8Q208C8

Цена: $122.2

есть в наличии

Описание

[Система Введение]

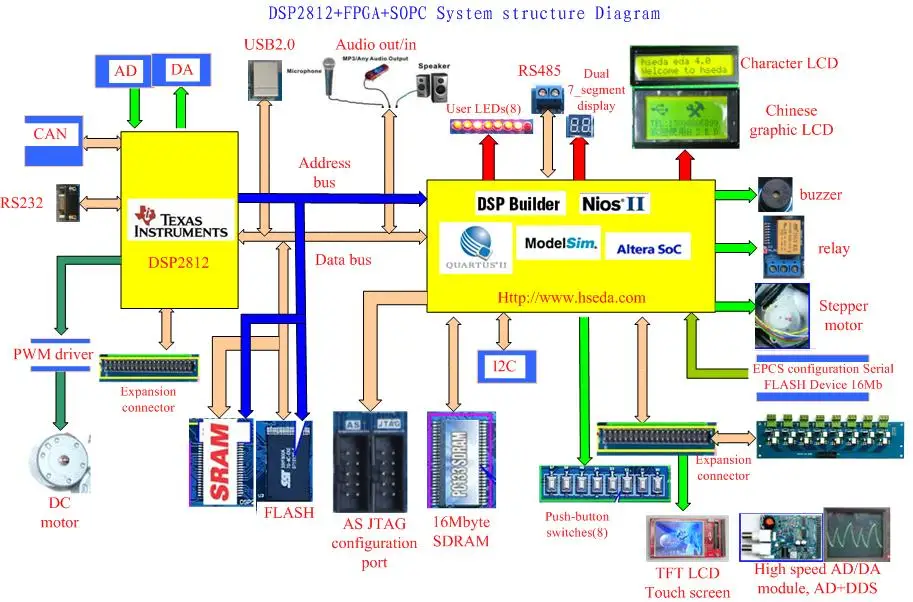

Этот набор основан на платформе TMS320F2812 + ep2c8q208c8 DSP + FPGA + NIOS обучения и развития, давая полную передачу гибкости и мощных функций TMS320F2812 и ALTERA CYCLONE II. руководство пользователя разработчика детально и легко понять, большое количество исходного кода легко начать (разделено на DSP И FPGA 2 части). Мы предоставляем полное ядро FPGA IP для пользователя, система выделяется и подключается через ядро IP, и пользователь может отрезать или добавить функцию в соответствии с потребностями. Поскольку наши периферийные устройства являются передовыми технологиями, такими как FPGA и DSP соединение, преобразование уровня, изоляция шины и разрешение, это очень удобно, гибко, лаконично, из-за этой структуры системы, таким образом, он работает и является стабильным, и может регулировать ток вождения, задержку, Стандарт выходного уровня каждого порта ввода/вывода в соответствии с требованиями. Он может в полной мере использовать большое количество ip-ядер CycloneII и PLL для высокоскоростных, высоких стабильных DSP + FPGA приложений, а также может использовать ALTERA DSP builder для генерации одного или нескольких ip-ядер DSP, так что может быть создана прикладная система многоядерный ЦП. Эти средства не доступны общим CPLD. Эта структура обеспечивает полную гибкость FPGA, высокую производительность и богатые ресурсы TMS320F2812. Макетная плата через профессионального старшего инженера в соответствии с высокочастотной системой проводки для ручного дизайна проводки, полного учета системы анти-помех и проблем петли, поэтому работа и стабильность. Это первый выбор для начинающих и исследователей, занимающихся исследованиями для изучения F2812 и FPGA.

Эта доска для развития для начинающих, чтобы узнать и использовать. Он также может быть встроен в продукт пользователя как системная плата для пользователей, чтобы сделать две разработки, чтобы сократить цикл разработки продукта.

[Системные ресурсы]

DSP процессор TMS320F2812, 32 бит с фиксированной точкой высокоскоростной цифровой процессор, максимальная рабочая частота 150 м;

Встроенная вспышка 128 K * 16 бит в чипе может использоваться для удобного закрепления пользовательских программ, а вспышка может быть зашифрована.

18 K * 16 бит SRAM встроен в пленку.

4 K * 16 bit BOOT rom встроен в чип.

1 K * 16 бит OTP rom встроен в чип.

Расширенная 256 K * 16 бит SRAM, IS61LV25616;

Расширение 512 K * 16 бит вспышки, SST39VF800 для облегчения пользователей для записи больших программ;

Размеры на 2-8 л сегментный цифровой трубок;

8 Светодиодный светильник, излучающий трубки, удобная индикация состояния;

Подтягиваются 9 автономных кнопок.

1 зуммер;

1 RS-232 интерфейс, который можно подключить к ПК для эксперимента.

1 способ RS-485 интерфейс, удобная пользовательская сеть, меры защиты портов;

1 интерфейс CAN2.0, удобный для пользовательских сетей;

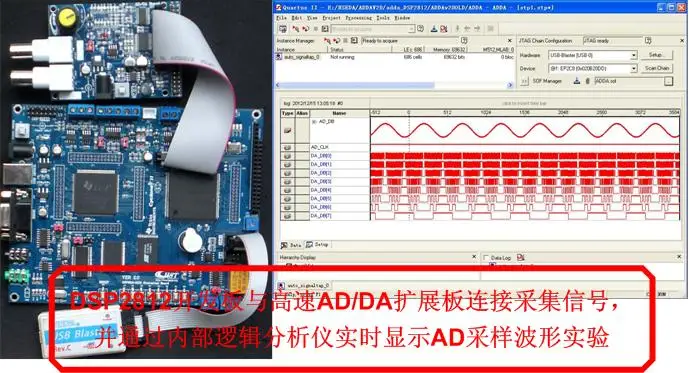

16 AD входной интерфейс (входной диапазон от 0 до 3 В), из которых во-первых, во-вторых можно подключить DA выход для проверки эксперимента, 3, 4 входа плюс ограничитель и amp после обработки, входной диапазон от 0 до 3 В (внимание не должно превышать диапазон!);

4 DA выходной интерфейс;

1 USB 2 интерфейс устройства, схема является взрослым чипом CY7C68013, обеспечивает готовую прошивку и код вызова ПК, может легко общаться с ПК, продолжать две разработки;

Разъем для наушников может легко воплотить в жизнь функцию воспроизведения.

Гнездо для микрофона используется для удобной записи.

12864 китайский Графический ЖК-дисплей интерфейс;

1602 символьный ЖК-интерфейс;

1 EEPROM, чип 24LC64, эксперимент по передаче данных с шиной IIC;

Интерфейс управления двигателем постоянного тока, дизайн с защитой от штепсельной вилки;

Интерфейс управления шаговым двигателем, дизайн с защитой от штепсельной вилки;

Интерфейс SPI, удобный для работы в сети;

Все выходные интерфейсы ШИМ были извлекены, и пользователи могут использовать их в соответствии с особыми требованиями.

Неэкранированный входной интерфейс источника прерывания для внешнего расширения 2 дорог.

Он может расширить до 5 каналов прерываемого интерфейса ввода источника, и 1 из них может быть активирован клавишами.

До 16 входных и 14 выходных интерфейсов, пользователи могут увеличить и удалить количество расширенного ввода/вывода путем изменения FPGA IP core, который мы предоставляем.

Автобуса открыт, линии передачи данных, адресная строка, линии управления и специальная функция pin все из них, что удобно для пользователей развиваться в два раза.

+ 5 В, 3,3 В, GND и другие точки тестирования мощности;

Источник питания поставляется непосредственно с помощью внешнего регулятора напряжения.

Независимый переключатель, управление электропитанием, удобное управление;

Четыре фиксированных отверстия удобны для установки и фиксации.

2 цифровых трубки, через интерфейс FPGA и DSP.

8 ввода ключа, через FPGA и цифровых сигнальных процессоров.

Предоставляется входной интерфейс источника прерывания.

Он обеспечивает Ручной Автоматический Сброс цепи для легкой отладки.

Обеспечить автобус открытым, линия данных, адресная линия, контрольная линия, специальная функция pin все свинца, удобный пользователь два раза развития.

Зуммером.

Блок питания может быть выбран перемычкой или интерфейсом USB.

1 Независимый реле, каждое реле нормально открытое и нормально закрытое, и Электрический шок был вызван для удобства пользователя.

Новый ALTERA cylconeII FPGA EP2C8Q208C8 используется для интерфейса и связи с DSP, а расширение порта ввода/вывода выделено отдельно.

Материнскую плату ячейки: 8256

Ввод/вывод: 139

Регистрирует: 8745

Дифференциальный I/O пар. 62

Битов памяти: 165888

M4K ram блоки: 36

Скорость Класс: 8

Plls: 2

Чип конфигурации FPGA EPCS16 16 M bit может удовлетворить большинство требований к конфигурации.

SDRAM 8 M X16bit 16 M байт памяти может сохранить временные собранные данные. Или сделать хранение данных в эксперименте NIOS.

[Дополнительную информацию и программное обеспечение]

1. Полная схема (формат PDF, гарантированно совпадают с печатной платой), быстро захватывает Применение ряда практичных интерфейсов.

2. Все эксперименты обеспечивают исходный код языка C и имеют подробные китайские пояснения.

3. Он-лайн горения вспышки методы и инструменты для того, чтобы укрепить инструкция собственный; в то же время

4. Руководство по чипу: обеспечивают чип информацию обо всех чипов на макетная плата;

5. Отправьте оригинальную среду разработки TI DSP CCS3.3;

6. Предоставьте эмулятор драйвер и других DSP книги и CD-ROM сопутствующие учебные материалы.

7. Мы делаем все, чтобы акробата, Bushound USB программное обеспечение для мониторинга шины, Sscom отладки помощник и других инструментов отладки.

8. Для того, чтобы отправить Altera загрузки линия схемой;

9. Мы делаем все, чтобы в программного обеспечения жидкокристаллического шрифта;

10. Предоставить TCP/IP соглашения объем: эта кнопка регулировки громкости 1 ~ 3;

11. Дайте спецификации USB документы;

12. Дайте CAN2.0 Спецификация документы;

13. Дайте U диск системы Описание документа;

14. Дайте FAT16, FAT32 системы документации;

15. Дайте UCOS-II источник трансплантата на F2812;

16. Дайте БПФ, елки, Новый год и другие расчет библиотеки;

17. Дайте TI полный чип посылка библиотеки.

18. Руководство пользователя: очень подробно, в том числе анализ схем, код, CCS2000 Быстрый старт руководство и т. д.

QUARTUS 8,0 + NIOS II IDE/SATA среды программирования полностью взломанная версия.

VHDL обычные коллекция

VHDL учебные пособия

135 случаев VERILOG обычные

VERILOG учебные пособия

DSPbuilder учебные пособия

Отправка серийный слушателем программное обеспечение для разработки RS232

Шрифт извлечения программное обеспечение и развитие ЖК-дисплей дисплея

USB2.0 хост компьютерной программой и исходный код

Полные системные ресурсы FPGA выделяют ядро IP и его исходный код.

Большое количество в комплекте NIOS развития учебные пособия. В том числе DSP, ЭПУ, SOPC видеоинструкции. «Избранное» позволяет легко овладеть DSP, FPGA, SOPC по разработке систем.

Вышеупомянутая информация предназначена для исследования только в том случае, и не для коммерческого использования.

Эксперимент путеводитель загрузки! (нажмите на \ tправая кнопка для того, чтобы сохранить ее)

[Код и экспериментов]

ПК класса демонстрация товара

Язык программирования ПК класса код обеспечивает графический интерфейс для Borland C + строителя. Позвонив по DLL функция библиотеки, потребитель должен свидетельствует о том, как получать и получать usb-кабель для передачи данных. Один и тот же DSP конец код также свидетельствует о том, как для чтения и записи данных. Пользователь может обратиться к этому вызова, например, для того, чтобы как можно скорее завершить его собственные разработки программы без его использования. Заботиться о деталях USB протокола.

USB2.0 верхнего компьютера передачи данных/беспроводного управления эксперимент (верхних слоев компьютер исходный код, благодаря чему Вы сможете легко инвестировать в разработке систем и приложение)

Полный FPGA IP драйвер и исходный код

Полная система материнскую плату интеграции и системы распределения ресурсов, пользователи могут собрать в соответствии со своими потребностями и их применение, таким образом, системные ресурсы соединены FPGA имеют соответствующие чтения и записи, адреса, и обеспечивают полную SDRAM (синхронное динамическое ОЗУ) ip-ядро, пользователи могут использовать для большой емкости системы хранения данных, Компания также предоставит пользователей с системой. Для более высокого качества и недорого высокоскоростной AD/DA расширения, на тонкопленочных транзисторах на тонкоплёночных транзисторах ЖК-дисплей расширения, изоляция оптопары для большой ток модуль ввода/вывода, перед размещением заказа рекомендуем внимательно ознакомиться с Вах Sheng ЭУР веб-сайта.

FPGA часть:

(Принимает VHDL код, и обеспечивает VHDL обычные коллекции, больше, чем 700 часто используемых процедур. VERILOG обычные 135 Чехлы, большое количество сжатого развития и учебные материалы, как видите, может не готово! Для справки пользователей.

Более опытной и видеоинструкции по будет запущено. Перед размещением заказа рекомендуем внимательно ознакомиться с Хуа Шэн ЭУР веб-сайта.

[Стандартная конфигурация]

1, DSP 2812 макетная плата one piece

2,5 V/1A импульсного источника питания

3, USB2.0 кабель-1 шт.;

4, RS232 связи (1 шт.)

5, LCD1602 жидкокристаллический 1

6. 1 двигатели постоянного тока

7. 1 DVD CD-ROM

Характеристики

- Бренд

- BETTERSHENGSUN

- Индивидуальное изготовление

- Да

- Test1

- 4

- Номер модели

- TMS320F2812

- Test4

- 4

Для покупки товара DSP2812 + FPGA + NIOS Совет по развитию TMS320F2812 EP2C8Q208C8 нажмите кнопку "купить сейчас".

Если вы хотите купить другой товар из категории электронные компоненты и комплектующие или электроника в наличии то перейдите по ссылкам вверху страницы.